Infineon TriCore

In this topic:

•AURIX Typical Debug and Trace Configurations

•AURIX Specific Trace Use Cases

The information provided in this chapter is intended to be used together with the CPU reference manual provided by the silicon vendor. This chapter assumes knowledge of the CPU functionality and the terminology and concepts defined and explained in the CPU reference manual. Basic knowledge of winIDEA is also necessary. This chapter deals with specifics and advanced details and it is not meant as a basic or introductory text.

•Setup - General settings to prepare winIDEA for debug session

•Flash programming - Additional configuration settings for internal flash programming

•Debug - Breakpoint access, SCR and HSM debug, Real-time memory access and more

•Analyzer - Trace, Aurora trace port, Trace templates, Profiler and Coverage

•Knowledge Base - Infineon TriCore specific problems solved

Getting started

Refer to Getting started Tutorials.

Debug Features

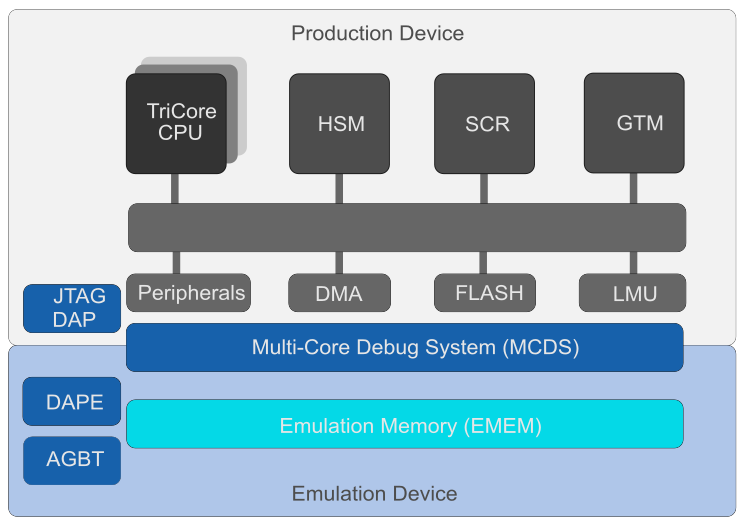

•DAP Standard (2-wire), DAP Wide (3-wire) and JTAG debug interface •DAPE trace interface on AURIX-2G and AURIX-3G •Hardware execution breakpoints •Unlimited software breakpoints •Hardware data access breakpoints •FLASH programming |

•Multi-core support •Real-time memory access •Hot Attach •Stopping peripherals (e.g. TIMERs) when stopped (CPU dependent) •On-Chip Trace support (miniMCDS, MCDS) •Aurora trace support (CPU dependent) |

AURIX Typical Debug and Trace Configurations

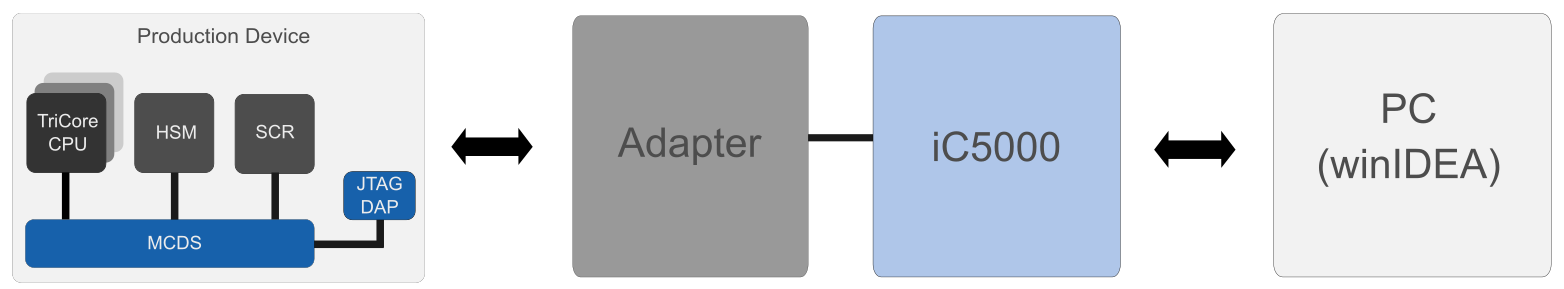

Debug: iC5000 & Debug Adapter

•Basic and compact system

•Debug Access via JTAG/DAP

•Optional Trace Support (EMEM, DAP, DAP Upload While Sampling - UWS) on Emulation Devices

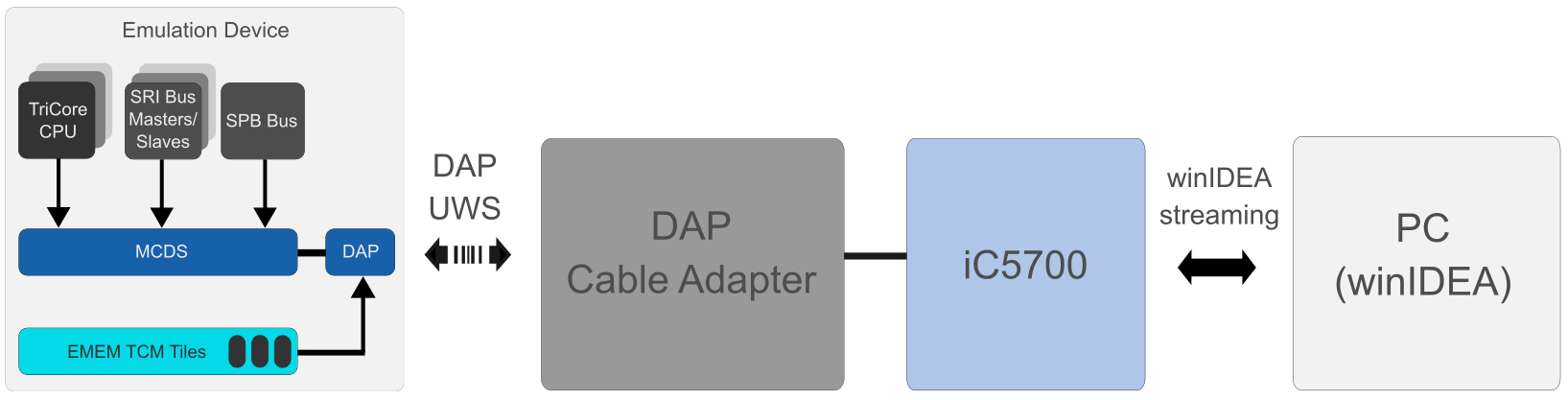

Debug and Trace via EMEM/DAP – iC5700 & Debug Adapter

•High-Performance, versatile System

•Debug Access via JTAG/DAP

•Trace Support via on-chip EMEM and DAP Streaming (Upload While Sampling - UWS)

•Debug Cable Adapter: DAP Clock up to 40 MHz, upload rate up to 5 MB/s

•iC5700: 1 GByte Trace Buffer, USB 3.0 / Ethernet

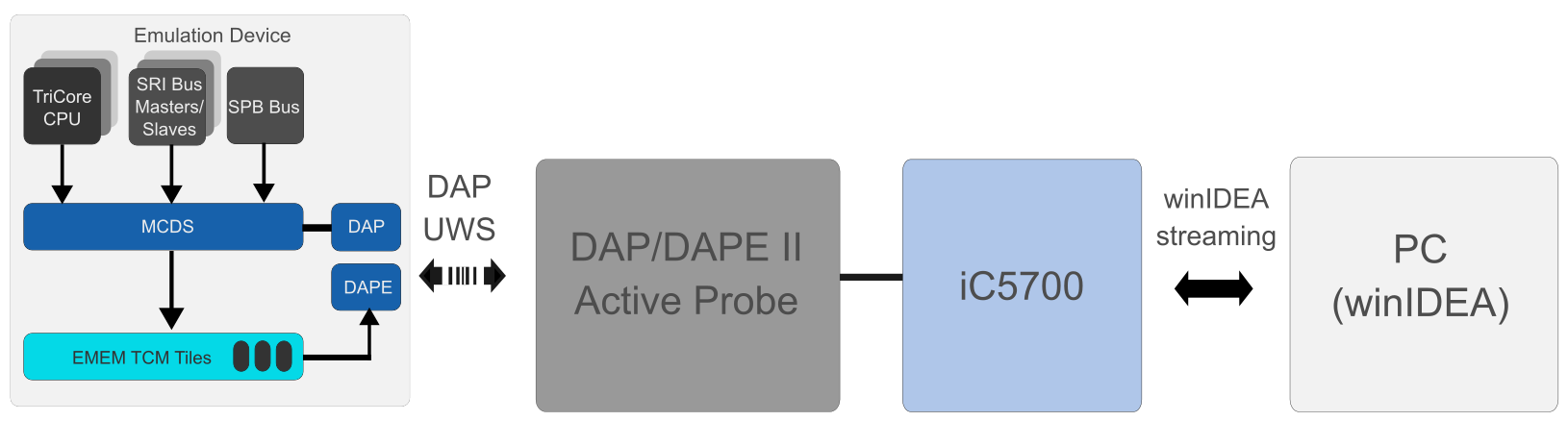

Debug and Trace via EMEM/DAP – iC5700 & Infineon DAP/DAPE II Active Probe

•High-Performance, versatile system

•Debug Access via JTAG/DAP

•Trace support via on-chip EMEM and DAP Streaming (Upload While Sampling - UWS)

•High-speed DAP Operation (up to 160 MHz)

•DAP + DAPE support for TC3xx, TC4xx Family

•Optional Add-On Modules:

oCAN/LIN Use case Configuration

•Synchronized Debug & Trace of multiple BlueBox

•Up to 5m FNet Cable to the iC5700

•Compact & robust design

•DAP/DAPE II Active Probe: Clock up to 160 MHz, upload rate up to 30MB/s

•iC5700: 1 GByte Trace Buffer, USB 3.0 / Ethernet

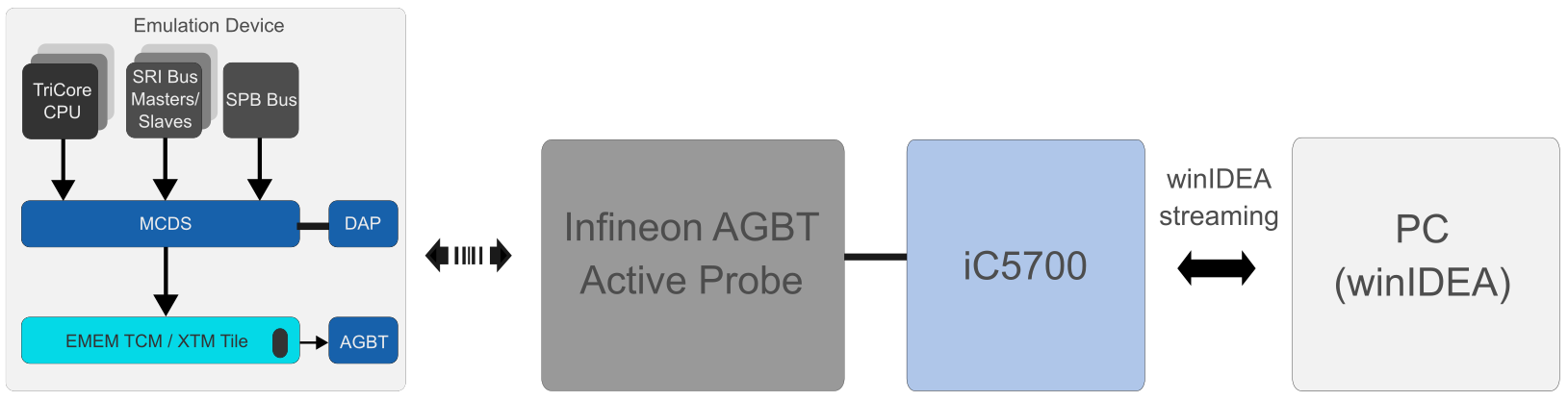

Debug and Trace via AGBT – iC5700 & Infineon AGBT Active Probe

•Highest Trace Performance, versatile System

•Ideally suited for long-term multi-core Program & OS Trace

•Debug Access via DAP

•Trace Support via on-chip EMEM or high-speed AGBT Streaming

•High-speed DAP Operation (up to 160 MHz)

•Optional Add-On Modules:

oCAN/LIN Use case Configuration

•Synchronized Debug & Trace of multiple BlueBox

•Up to 5m FNet Cable to the iC5700

•Compact & robust design

•Active Probe Infineon AGBT: Bitrate up to 2.5Gbps, upload rate app. 300 MB/s

•iC5700: 1 GByte Trace Buffer, USB 3.0 / Ethernet

AURIX Specific Trace Use Cases

DAP Streaming - Upload While Sampling (UWS)

•Allows Upload of Trace Data from EMEM to Host PC (winIDEA) while Trace Recording is running

•If Upload Bandwidth is higher than the Trace Data Generation Rate, Upload While Sampling can run infinitely

•Ideally suited for (long-term) OS Profiling

•DAP/DAPE II Active Probe allows DAP Operation at maximum 160 MHz for optimized Streaming Bandwidth

•A minimum of 2 (better 3) EMEM Tiles need to be available for Trace

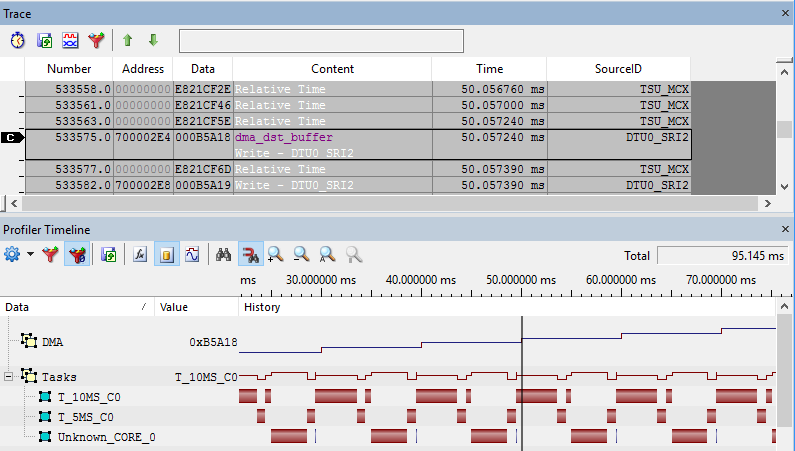

DMA Trace

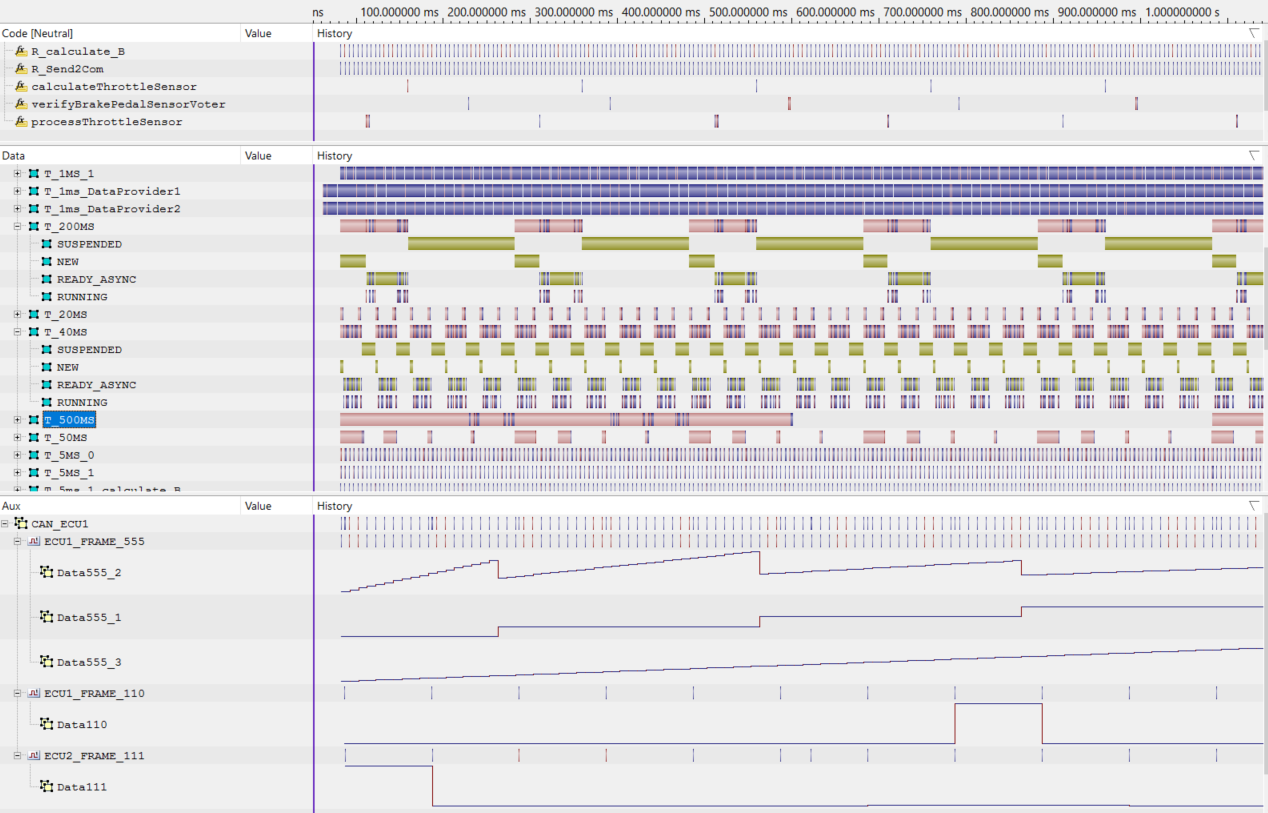

The winIDEA Trace Analyzer allows full utilization of the extremely versatile configuration options of the AURIX MCDS On-Chip Trace functionality. This allows, for instance, tracing of SRI bus transactions of specific bus masters such as the DMA controller along with the CPU instruction trace or OS task trace.

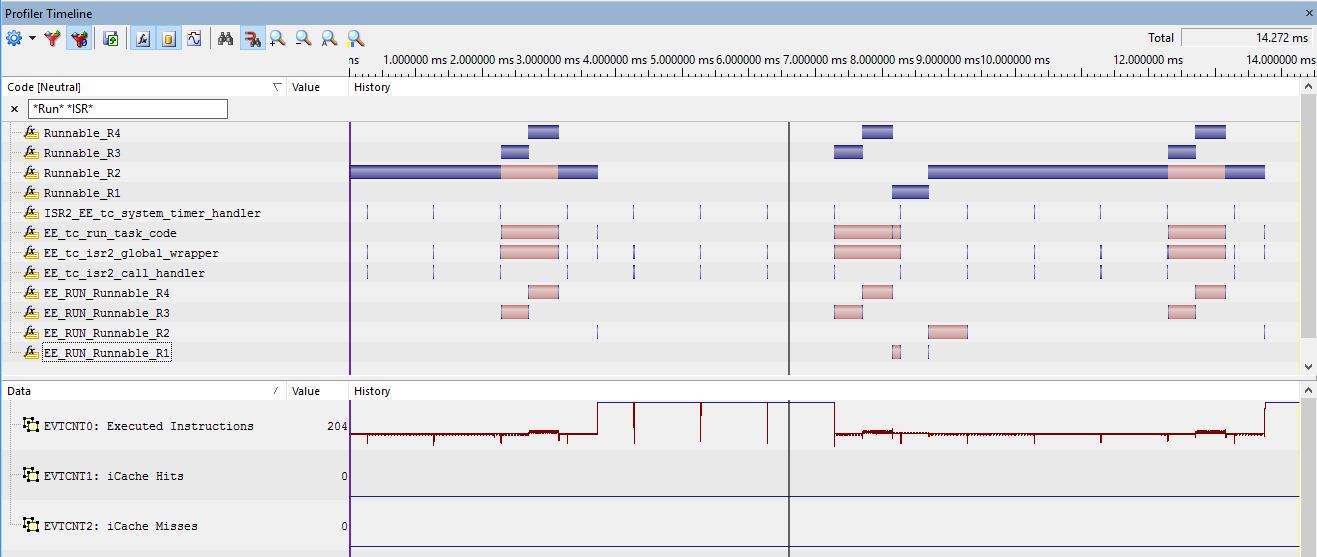

Trace of CPU Performance Counters

The winIDEA Trace Analyzer allows full utilization of the extremely versatile configuration options of the AURIX MCDS on-chip Trace functionality. This allows, for instance, a real-time trace of the CPU-internal performance counters, measuring performance parameters such as Instruction Execution rate, Cache Hit / Miss rates, etc.

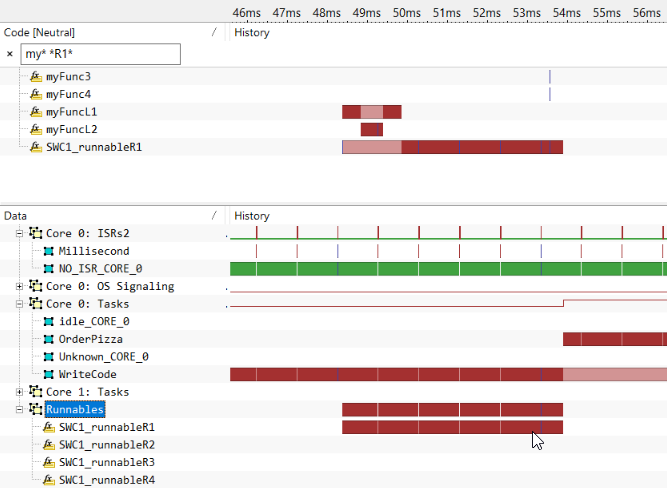

Compact Function Trace (CFT)

CFT is a feature of the MCDS Processor Observation Block (POB). Its goal is to reduce trace bandwidth, while providing the ability to trace function execution. Trace messages are only generated upon a function call and function return. Also, indirect calls (e.g. Interrupt Service Routines) generate a trace message.

This concept brings big savings especially when long functions are executed, as all instruction execution inside the function generates no trace data. However, the CFT concept relies on consistent function call-return sequences. Certain compiler optimizations “violate” this constraint and thus CFT-based function profiling may not be applicable.

ADIO & CAN Trace

A trace recording via DAP UWS allows a time correlation with Analog/Digital or CAN/LIN bus signals captured by means of the ADIO and/or CAN/LIN Add-On Module of the iC5700.

More resources

•Infineon AURIX™ Microcontrollers dedicated website